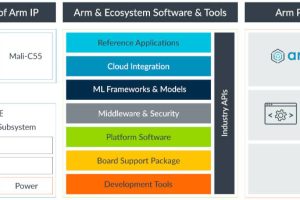

Arm has announced its most powerful microcontroller-grade neural processor, which will reach 4Top/s in its maximum configuration and is 20% more power efficient that its previous neural processors. Named Ethos-U85 and configurable with between 128 and 2,048 MACs, it is intended to have enough performance to locally run heavy AI algorithms such as ‘transformers’, as well as convolutional neural networks. ...

EDA and IP

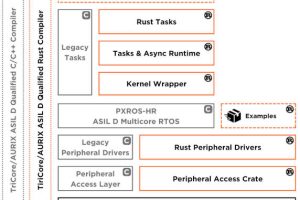

Embedded World: ASIL D qualified Rust compiler for Infineon TriCore processors

Infineon has lined up a Rust programming language compiler for two of its TriCore architecture processor families: the existing TC3x and forthcoming TC4x. “Rust, with its unique memory safety features, has emerged as a viable complement or potential substitute for C/C++ in automotive software development,” according to the company. Working with Infineon, HighTec EDV-Systeme has released an ISO 26262 ASIL ...

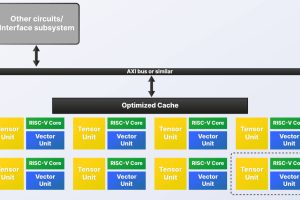

Semidynamics proposes modular RISC-V architecture for scalable AI processing

Barcelona-based Semidynamics is aiming at next-generation AI chips and algorithms such as transformer with intellectual property called ‘All-In-One AI’. Rather than having on the same IC a multi-core CPU, a multi-core GPU for vector processing and a multi-core neural processor for tensor processing, it is advocating multiple instances of a block consisting of one out-of-order 64bit RISC-V CPU, one (GPU-like) ...

Accelerated RISC-V core optimised for edge AI and cryptography

Red Semiconductor has announced RISC-V instruction set extensions, and a hardware design, for edge AI and cryptography in asics and FPGAs. The hardware, called ‘VISC’, is an accelerated RISC-V core that “optimises complex mathematical algorithms for parallel execution in its reconfiguration hardware engine”, according to Red, which claims: “The VISC ISA [instruction set] enables developers to describe complex algorithms in ...

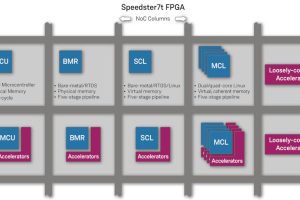

Linux-capable RISC-V soft cores for Achronix FPGAs

Achronix has teamed up with Bluespec to offer a family of Linux-capable RISC-V soft processors for the Speedster7t FPGA family. “Bluespec’s RISC-V processors now integrate into the Achronix 2D network-on-chip architecture, simplifying integration and enabling engineers to add scalable processing to their designs,” according to Achronix. “The network allows multiple instances of the RISC-V core to be added, and relocated ...

Nvidia packages inference to deliver generative AI for healthcare

Optimised packages of AI models and workflows with API have been packaged as NIMs (Nvidia Inference Microservices) which developers can use as building blocks to develop generative AI for healthcare, from drug discovery, med-tech and digital health products. Nvidia announced 25 NIMs at its developer conference, GTC 2024, offering advanced imaging, natural language and speech recognition, digital biology generation, prediction ...

Nvidia offers Omniverse Cloud as APIs

A new take on the concept of digital twins was announced by Nvidia at its developer conference in San Jose this week, as founder and CEO, Jensen Huang announced that the company’s Omniverse Cloud will be available as APIs (application programming interfaces). Customers will be able to use these APIs to design, simulate, test and build physically based digital twins ...

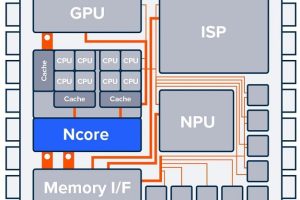

Network-on-chip supports Arm v9 and automotive functional safety

Arteris is supporting Armv9 automotive cores and ASIL D functional safety with release 3.6 of its Ncore cache coherent network-on-chip. “In 2020, Arteris announced a partnership with Arm and the alignment of our roadmaps to support CHI-E and ASIL B and ASIL D safety,” Arteris told Electronics Weekly. “We confirm the expansion of that partnership with a pre-validation of our ...

Emulation and prototyping trio addresses AI, ML and hyperscale computing

Siemens EDA has announced three products, for emulation, evaluation and software prototyping for data centres and servers. The Veloce CS consists of the Strato CS hardware, for emulation, the Primo CS hardware for enterprise prototyping and proFPGA CS hardware for software prototyping. According to the company, the hardware-assisted verification and validation system can accelerate verification and validation cycles by up ...

Training-grade PDK for 2nm gate-all-around ICs

Imec has launched an early-access process design kit for the N2 (2nm ICs) node. “The PDK will enable virtual digital designs in imec’s N2 technology, including backside power delivery network,” according to the Belgion semiconductor research lab. “This will give academia and industry the tools to train the semiconductor experts of tomorrow and enable the industry to transition their products ...

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News